|

|

|

Intel Celeron M 500er Serie

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Systemtakt / Systembustakt:

|

|

|

133 MHz / 533 MHz quad-pumped (bis zu 4,3 GB/sek Datentransfer)

|

|

|

|

|

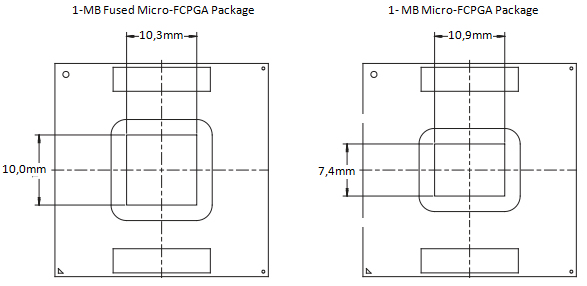

478-pin micro Flip-Chip Pin Grid Array (mFC-PGA)

|

|

|

|

|

|

|

|

QVTB, QVTC, QXWY, SLA2F, SLA47

|

|

|

|

|

|

|

|

Powermanagement

System Management Mode

Taktkontrolle und Low-Power States

# Core Low Power States

- C1/AutoHALT Powerdown state

- C1/MWAIT Powerdown state

- Core C2 State

- Core C3 State

# Package Low Power States

- Stop Grant State

- Stop Grant snoop state

- Sleep state

- Deep sleep state

FSB Low Power Enhancements

- Dynamic on-die termination disabling

- Low VCCP (I/O termination voltage)

Processor Power Status Indicator (PSI#) Signal

|

|

|

|

|

|

Temperaturbereich (min/max):

|

|

|

|

Verlustleistung (min/max):

|

|

|

6,8 Watt (Deep Sleep) / 45,31 Watt

|

|

|

|

|

|

|

|

|

|

Intel Core Mikroarchitektur (1. Generation)

14-stufige Pipeline

Dynamische Ausführung

Extended Memory 64 Technologie

- 64 Bit flat virtual address space

- 64 Bit pointers

- 64 Bit wide general purpose registers

- 64 Bit integer support

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Befehlssatzerweiterungen:

|

|

|

MMX, SSE, SSE2, SSE3 und SSSE3

|

|

|

|

|

|

|

|

|

|

|

|

- 8-way set-associative

- jeweils 32 KB Befehls- und Datencache

|

|

|

|

|

- advanced transfer Cache

- 4-way set-associative

- gemeinsamer Befehls- und Datencache

|

|

|

Enhanced Floating Point Unit

Address Bus ( (überträgt zwei Datenpakete pro Takt)

Quad-pumped FSB (überträgt vier Datenpakete pro Takt)

Prozessor Thermal Features

- Thermal Monitor

- Digital Thermal Sensor

- Out of specification detection

- PROCHOT# Signal Pin

- Thermal Diode

|

|

|

|

|

|

|

|

Dieser Prozessor unterstützt sowohl 32- als auch 64-Bit Betriebssysteme und Software zu 100%

|

|

|

|

|